**ACT361**

Rev 8, 14-Nov-12

## High Performance *ActivePSR™* Primary Switching Regulator

#### **FEATURES**

- Patented Primary Side Regulation Technology

- No Opto-Coupler

- Best-in-Class Constant Voltage, Constant Current Accuracy

- Low EMI

- Proprietary Fast Startup Circuit

- Built-in Soft-Start Circuit

- Integrated Line and Primary Inductance Compensation

- Integrated Programmable Output Cord Resistance Compensation

- Line Under-Voltage, Output Over-Voltage, Output Short-Circuit and Over-Temperature Protection

- Complies with all Global Energy Efficiency and CEC Average Efficiency Standards

- Adjustable power from 2W to 7W

- Minimum External Components

- Tiny SOT23-6 Package

#### APPLICATIONS

- Chargers for Cell Phones, PDAs, MP3, Portable Media Players, DSCs, and Other Portable Devices and Appliances

- RCC Adapter Replacements

- Linear Adapter Replacements

- Standby and Auxiliary Supplies

#### GENERAL DESCRIPTION

The ACT361 belongs to the high performance patented *ActivePSR<sup>TM</sup>* Family of Universal-input AC/DC off-line controllers for battery charger and adapter applications. It is designed for flyback topology working in discontinuous conduction mode (DCM). The ACT361 meets all of the global energy efficiency regulations (CEC, European Blue Angel, and US Energy Star standards) while using very few external components.

The ACT361 ensures safe operation with complete protection against all fault conditions. Built-in protection circuitry is provided for output short-circuit, output over-voltage, line under-voltage, and over temperature conditions.

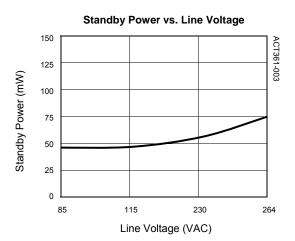

The ACT361 *ActivePSR*<sup>TM</sup> is optimized for high performance, cost-sensitive applications, and utilizes Active-Semi's proprietary primary-side feedback architecture to provide accurate constant voltage, constant current (CV/CC) regulation without the need of an opto-coupler or reference device. Integrated line and primary inductance compensation circuitry provides accurate constant current operation despite wide variations in line voltage and primary inductance. Integrated output cord resistance compensation further enhances output accuracy. The ACT361 achieves excellent regulation and transient response, yet requires less than 150mW of standby power.

The ACT361 is optimized for 2W to 7W applications. It is available in space-saving 6 pin SOT23-6 package.

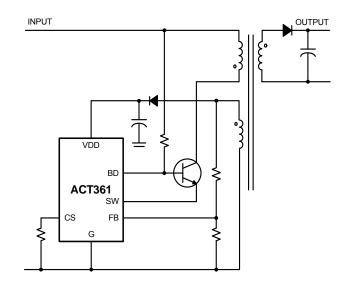

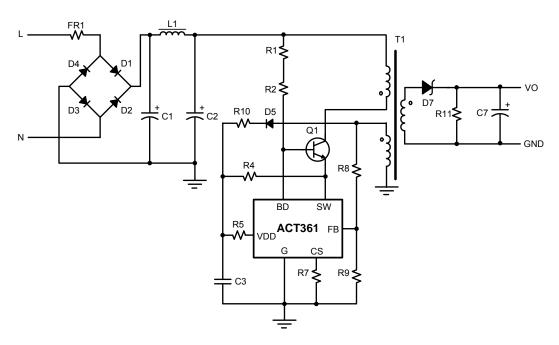

Figure 1: Simplified Application Circuit

## **ORDERING INFORMATION**

| PART NUMBER | TEMPERATURE RANGE | PACKAGE | PINS | PACKING<br>METHOD | TOP MARK |

|-------------|-------------------|---------|------|-------------------|----------|

| ACT361US-T  | -40°C to 85°C     | SOT23-6 | 6    | TAPE & REEL       | FSCR     |

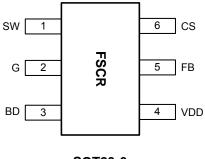

### **PIN CONFIGURATION**

SOT23-6 ACT361US-T

### **PIN DESCRIPTIONS**

| PIN | NAME | DESCRIPTION                                                                                                                                                                                                                                                         |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SW   | Switch Drive. Switch node for the external NPN transistor. Connect this pin to the external power NPN's emitter. This pin also supplies current to VDD during startup.                                                                                              |

| 2   | G    | Ground.                                                                                                                                                                                                                                                             |

| 3   | BD   | Base Drive. Base driver for the external NPN transistor.                                                                                                                                                                                                            |

| 4   | VDD  | Power Supply. This pin provides bias power for the IC during startup and steady state operation.                                                                                                                                                                    |

| 5   | FB   | Feedback Pin. Connect this pin to a resistor divider network from the auxiliary winding.                                                                                                                                                                            |

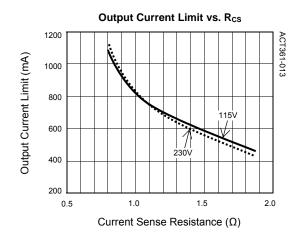

| 6   | CS   | Current Sense Pin. Connect an external resistor ( $R_{CS}$ ) between this pin and ground to set peak current limit for the primary switch. The peak current limit is set by (0.396V × 0.9) / $R_{CS}$ . For more detailed information, see Application Information. |

# **ABSOLUTE MAXIMUM RATINGS®**

| PARAMETER                                                               | VALUE              | UNIT |

|-------------------------------------------------------------------------|--------------------|------|

| VDD, BD, SW to G                                                        | -0.3 to +28        | V    |

| Maximum Continuous VDD Current                                          | 100                | mA   |

| FB, CS to G                                                             | -0.3 to +6         | V    |

| Continuous SW Current                                                   | Internally limited | Α    |

| Maximum Power Dissipation (derate 4.5mW/°C above T <sub>A</sub> = 50°C) | 0.45               | W    |

| Junction to Ambient Thermal Resistance $(\theta_{JA})$                  | 220                | °C/W |

| Operating Junction Temperature                                          | -40 to 150         | °C   |

| Storage Junction                                                        | -55 to 150         | °C   |

| Lead Temperature (Soldering, 10 sec)                                    | 300                | °C   |

①: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}$  = 14V,  $V_{OUT}$  = 5V,  $L_P$  = 2.3mH,  $N_P$  = 140,  $N_S$  = 10,  $N_A$  = 27,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                            | SYMBOL             | TEST CONDITIONS                         | MIN   | TYP   | MAX   | UNIT  |  |

|--------------------------------------|--------------------|-----------------------------------------|-------|-------|-------|-------|--|

| Supply                               | '                  |                                         |       |       |       |       |  |

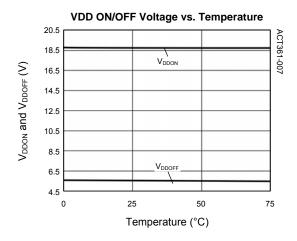

| VDD Turn-On Voltage                  | $V_{DDON}$         | V <sub>DD</sub> Rising from 0V          | 17.6  | 18.6  | 19.6  | V     |  |

| VDD Turn-Off Voltage                 | $V_{DDOFF}$        | V <sub>DD</sub> Falling after Turn-on   | 5.25  | 5.5   | 5.75  | V     |  |

| Supply Current                       | I <sub>DD</sub>    | V <sub>DD</sub> = 14V, after Turn-on    |       | 1     | 2     | mA    |  |

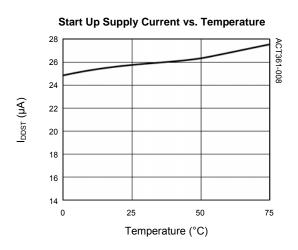

| Start Up Supply Current              | I <sub>DDST</sub>  | V <sub>DD</sub> = 14V, before Turn-on   |       | 25    | 45    | μA    |  |

| BD Current during Startup            | I <sub>BDST</sub>  |                                         |       |       | 1     | μA    |  |

| Internal Soft Startup Time           |                    |                                         |       | 10    |       | ms    |  |

| Oscillator                           |                    |                                         |       |       |       |       |  |

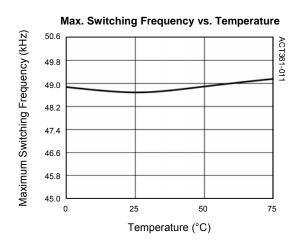

| Switching Frequency                  | f                  | 100% V <sub>OUTCV</sub> @ full load     | 42    |       | kHz   |       |  |

| Switching Frequency                  | $f_{SW}$           | 25% V <sub>OUTCV</sub> @ full load      |       | 21    |       | NI IZ |  |

| Maximum Switching Frequency          | F <sub>CLAMP</sub> |                                         | 45    |       | 55    | kHz   |  |

| Maximum Duty Cycle                   | $D_{MAX}$          |                                         | 70    | 75    | 80    | %     |  |

| Feedback                             |                    |                                         |       |       |       |       |  |

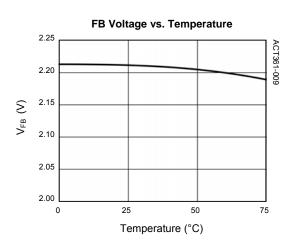

| Effective FB Voltage                 | $V_{FB}$           |                                         | 2.176 | 2.200 | 2.224 | V     |  |

| FB Leakage Current                   | I <sub>FBLK</sub>  |                                         |       |       | 100   | nA    |  |

|                                      |                    | No R <sub>CORD</sub> between VDD and SW | 0 3   |       |       |       |  |

|                                      |                    | R <sub>CORD</sub> = 300k                |       |       | %     |       |  |

| Output Cable Resistance Compensation | $DV_COMP$          | R <sub>CORD</sub> = 150k                | 6     |       |       |       |  |

|                                      |                    | R <sub>CORD</sub> = 75k                 |       | 9     |       |       |  |

|                                      |                    | R <sub>CORD</sub> = 33k                 |       | 12    |       |       |  |

#### **ELECTRICAL CHARACTERISTICS CONT'D**

$(V_{DD}$  = 14V,  $V_{OUT}$  = 5V,  $L_P$  = 2.3mH,  $N_P$  = 140,  $N_S$  = 10,  $N_A$  = 27,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                    | SYMBOL              | TEST CONDITIONS            | MIN                     | TYP                     | MAX                     | UNIT |

|------------------------------|---------------------|----------------------------|-------------------------|-------------------------|-------------------------|------|

| Current Limit                |                     |                            |                         |                         |                         |      |

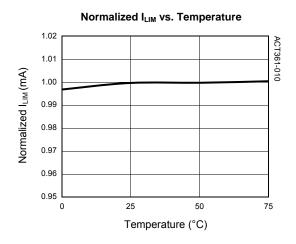

| SW Current Limit Range       | I <sub>LIM</sub>    |                            | 100                     |                         | 600                     | mA   |

| CS Current Limit Threshold   | V <sub>CSLIM</sub>  | t <sub>OFF_DELAY</sub> = 0 | 380                     | 396                     | 412                     | mV   |

| Leading Edge Blanking Time   |                     |                            | 200                     | 300                     |                         | ns   |

| Driver Outputs               | -                   |                            |                         |                         |                         |      |

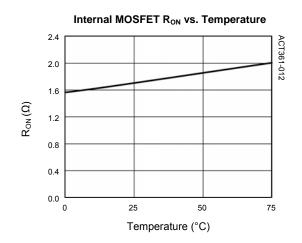

| Switch ON-Resistance         | R <sub>ON</sub>     | I <sub>SW</sub> = 50mA     |                         | 1.6                     |                         | Ω    |

| SW Off Leakage Current       |                     | $V_{SW} = V_{DD} = 22V$    |                         |                         | 5                       | μΑ   |

| Protection                   | -                   |                            |                         |                         |                         |      |

| VDD Latch-Off Voltage        | $V_{DDOVP}$         |                            | V <sub>DDON</sub><br>+2 | V <sub>DDON</sub><br>+3 | V <sub>DDON</sub><br>+4 | V    |

| Thermal Shutdown Temperature |                     |                            |                         | 135                     |                         | °C   |

| Thermal Hysteresis           |                     |                            |                         | 20                      |                         | °C   |

| Line UVLO                    | I <sub>FBUVLO</sub> |                            |                         | 116                     |                         | μA   |

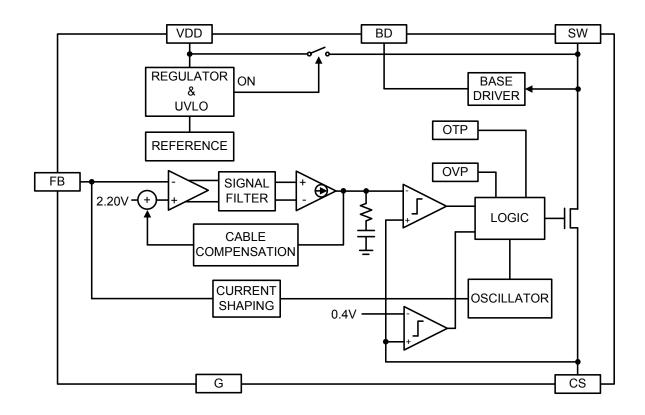

### **FUNCTIONAL BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

As shown in the Functional Block Diagram, to regulate the output voltage in CV (constant voltage) mode, the ACT361 compares the feedback voltage at FB pin to the internal reference and generates an error signal to the pre-amplifier. The error signal, after filtering out the switching transients and compensated with the internal compensation network, modulates the external NPN transistor peak current at CS pin with current mode PFWM (Pulse Frequency and Width Modulation) control. To regulate the output current in CC (constant current) mode, the oscillator frequency is modulated by the output voltage.

SW is a driver output that drives the emitter of an external high voltage NPN transistor. This base-emitter-drive method makes the drive circuit the most efficient.

#### **Fast Startup**

VDD is the power supply terminal for the ACT361. During startup, the ACT361 typically draws only 20µA supply current. The startup resistor from the rectified high voltage DC rail supplies current to the base of the NPN transistor. This results in an amplified emitter current to VDD through the SW pin via Active-Semi's proprietary fast-startup circuitry until it exceeds the V<sub>DDON</sub> threshold 19V. At this point, the ACT361 enters internal startup mode with the peak current limit ramping up in 10ms. After switching starts, the output voltage begins to rise. The VDD bypass capacitor must supply the ACT361 internal circuitry and the NPN base drive until the output voltage is high enough to sustain VDD through the auxiliary winding. The VDDOFF threshold is 5.5V; therefore, the voltage on the VDD capacitor must remain above 5.5V while the output is charging up.

#### **Constant Voltage (CV) Mode Operation**

In constant voltage operation, the ACT361 captures the auxiliary flyback signal at FB pin through a resistor divider network R8 and R9 in Figure 6. The signal at FB pin is pre-amplified against the internal reference voltage, and the secondary side output voltage is extracted based on Active-Semi's proprietary filter architecture.

This error signal is then amplified by the internal error amplifier. When the secondary output voltage is above regulation, the error amplifier output voltage decreases to reduce the switch current. When the secondary output voltage is below regulation, the error amplifier output voltage

increases to ramp up the switch current to bring the secondary output back to regulation. The output regulation voltage is determined by the following relationship:

$$V_{OUTCV} = 2.20V \times \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) \times \frac{N_S}{N_A} - V_D$$

(1)

where  $R_{FB1}$  (R8) and  $R_{FB2}$  (R9) are top and bottom feedback resistor,  $N_{S}$  and  $N_{A}$  are numbers of transformer secondary and auxiliary turns, and  $V_{D}$  is the rectifier diode forward drop voltage at approximately 0.1A bias.

#### Standby (No Load) Mode

In no load standby mode, the ACT361 oscillator frequency is further reduced to a minimum frequency while the current pulse is reduced to a minimum level to minimize standby power. The actual minimum switching frequency is programmable with an output preload resistor.

#### **Loop Compensation**

The ACT361 integrates loop compensation circuitry for simplified application design, optimized transient response, and minimal external components.

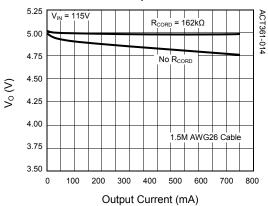

#### **Output Cable Resistance Compensation**

The ACT361 provides programmable output cable resistance compensation during constant voltage regulation, monotonically adding an output voltage correction up to predetermined percentage at full power. There are four levels to program the output cable compensation by connecting a resistor (R4 in Figure 6) from the SW pin to VDD pin. The percentage at full power is programmable to be 3%, 6%, 9% or 12%, and by using a resistor value of 300k, 150k, 75k or 33k respectively. If there is no resistor connection, there is no cord compensation.

This feature allows for better output voltage accuracy by compensating for the output voltage droop due to the output cable resistance.

#### **Constant Current (CC) Mode Operation**

When the secondary output current reaches a level set by the internal current limiting circuit, the ACT361 enters current limit condition and causes the secondary output voltage to drop. As the output voltage decreases, so does the flyback voltage in a proportional manner. An internal current shaping circuitry adjusts the switching frequency based on the flyback voltage so that the transferred power remains proportional to the output voltage, resulting

#### FUNCTIONAL DESCRIPTION CONT'D

in a constant secondary side output current profile. The energy transferred to the output during each switching cycle is  $\frac{1}{2}(L_P \times I_{LIM}^2) \times \eta$ , where  $L_P$  is the transformer primary inductance,  $I_{LIM}$  is the primary peak current, and  $\eta$  is the conversion efficiency. From this formula, the constant output current can be derived:

$$I_{OUTCC} = \frac{1}{2} \times L_P \times \left(\frac{0.396V \times 0.9}{R_{CS}}\right)^2 \times \left(\frac{\eta \times f_{SW}}{V_{OUTCV}}\right)$$

(2)

where  $f_{SW}$  is the switching frequency and  $V_{OUTCV}$  is the nominal secondary output voltage.

The constant current operation typically extends down to lower than 40% of nominal output voltage regulation.

#### **Primary Inductance Compensation**

The ACT361 integrates a built-in proprietary (patent-pending) primary inductance compensation circuit to maintain constant current regulation despite variations in transformer manufacturing. The compensated range is ±7%.

#### **Primary Inductor Current Limit Compensation**

The ACT361 integrates a primary inductor peak current limit compensation circuit to achieve constant input power over line and load ranges.

#### **Protection**

The ACT361 incorporates multiple protection functions including over-voltage, over-current and over-temperature.

#### **Output Short Circuit Protection**

When the secondary side output is short circuited, the ACT361 enters hiccup mode operation. In this condition, the VDD voltage drops below the  $V_{\text{DDOFF}}$  threshold and the auxiliary supply voltage collapses. This turns off the ACT361 and causes it to restart. This hiccup behavior continues until the short circuit is removed.

#### **Output Over Voltage Protection**

The ACT361 includes output over-voltage protection circuitry, which shuts down the IC when the output voltage is 40% above the normal regulation voltage for 4 consecutive switching cycles. The ACT361 enters hiccup mode when an output over voltage fault is detected.

#### **Over Temperature Shutdown**

The thermal shutdown circuitry detects the ACT361

die temperature. The typical over temperature threshold is 135°C with 20°C hysteresis. When the die temperature rises above this threshold the ACT361 is disabled until the die temperature falls by 20°C, at which point the ACT361 is re-enabled.

#### TYPICAL APPLICATION

#### **Design Example**

The design example below gives the procedure for a DCM flyback converter using the ACT361. Refer to Application Circuit in Figure 6, the design for a charger application starts with the following specification:

| Input Voltage Range                          | 85VAC - 265VAC, 50/60Hz |

|----------------------------------------------|-------------------------|

| Output Power, Po                             | 3.5W                    |

| Output Voltage, V <sub>OUTCV</sub>           | 5.0V                    |

| Full Load Current, I <sub>OUTFL</sub>        | 0.7A                    |

| OCP Current, I <sub>OUTMAX</sub>             | 0.9A                    |

| Transformer Efficiency, $\eta_{\text{xfm}}$  | 0.9                     |

| System Efficiency CC, $\eta_{\text{system}}$ | 0.69                    |

| System Efficiency CV, η                      | 0.7                     |

The operation for the circuit shown in Figure 6 is as follows: the rectifier bridge D1-D4 and the capacitor C1/C2 convert the AC line voltage to DC. This voltage supplies the primary winding of the transformer T1 and the startup resistor R1/R2. The primary power current path is formed by the transformer's primary winding, the NPN transistor, the ACT361 internal MOSFET and the current sense resistor R7. The network consisting of capacitor C3 and diode D5 provides a VDD supply voltage for ACT361 from the auxiliary winding of the transformer. C3 is the decoupling capacitor of the supply voltage and energy storage component for startup. The diode D7 and the capacitor C7 rectifies and filters the output voltage. The resistor divider consisting of R8 and R9 programs the output voltage.

The minimum and maximum DC input voltages can be calculated:

$$V_{INDCMIN} = \sqrt{2V_{ACMIN}^2 - \frac{2P_{OUT}(\frac{1}{2f_L} - t_C)}{\eta \times C_{IN}}}$$

$$= \sqrt{2 \times 85^2 - \frac{2 \times 3.5(\frac{1}{2 \times 50} - 3.5ms)}{70\% \times 2 \times 4.7\mu F}} \approx 90V$$

(3)

$$V_{INDCMAX} = \sqrt{2} \times V_{ACMAX} = \sqrt{2} \times 265 = 375V \tag{4}$$

### TYPICAL APPLICATION CONT'D

where  $\eta$  is the estimated circuit efficiency,  $f_L$  is the line frequency,  $t_C$  is the estimated rectifier conduction time,  $C_{IN}$  is empirically selected to be 2  $\times$  4.7µF electrolytic capacitors based on the 3µF/W rule of thumb.

When the transistor is turned off, the voltage on the transistor's collector consists of the input voltage and the reflected voltage from the transformer's secondary winding. There is a ringing on the rising top edge of the flyback voltage due to the leakage inductance of the transformer. This ringing is clamped by a RCD network if it is used. Design this clamped voltage as 50V below the breakdown of the NPN transistor. The flyback voltage has to be considered with selection of the maximum reverse voltage rating of secondary rectifier diode. If a 40V Schottky diode is used, then the flyback voltage can be calculated:

$$V_{RO} = \frac{V_{INDCMAX} \times (V_{OUTCV} + V_{DS})}{V_{DREV} - V_{OUTCV}} = \frac{375 \times (5 + 0.3)}{40 \times 0.8 - 5} = 73.5V$$

(5)

where  $V_{DS}$  is the Schottky diode forward voltage,  $V_{DREV}$  is the maximum reverse voltage rating of the diode and  $V_{OUTCV}$  is the output voltage.

The maximum duty cycle is set to be 35% at low line voltage  $85V_{AC}$  and the circuit efficiency is estimated to be 70%. Then the full load input current is:

$$I_{IN} = \frac{V_{OUTCV} \times I_{OUTPL}}{V_{INDCMIN} \times \eta} = \frac{5 \times 0.7}{90 \times 70\%} = 55.56 \text{mA}$$

(6)

The maximum input primary peak current at full load base on duty of 35%:

$$I_{PK} = \frac{2 \times I_{IN}}{D} = \frac{2 \times 55.56}{35\%} = 318 \text{ mA}$$

(7)

The primary inductance of the transformer:

$$L_{P} = \frac{V_{INDCMIN} \times D}{I_{PK} \times f_{SW}} = \frac{90 \times 35\%}{318 \text{ mA} \times 42 \text{ kHz}} = 2.35 \text{ mH}$$

(8)

Where f<sub>SW</sub> is the full load frequency at CV mode.

The primary to secondary turns ratio N<sub>P</sub>/N<sub>S</sub>:

$$\frac{N_P}{N_S} = \frac{V_{RO}}{V_{OUTCV} + V_{DS}} = \frac{74}{5 + 0.3} = 14$$

(9)

The auxiliary to secondary turns ratio N<sub>A</sub>/N<sub>S</sub>:

$$\frac{N_A}{N_S} = \frac{V_{DD} + V_{DA}}{V_{OUTCV} + V_{DS} + V_{CORD}} = \frac{14.5 + 0.7}{5 + 0.30 + 0.3} = 2.7$$

(10)

Where  $V_{\text{DA}}$  is the diode forward voltage of the auxiliary side.

An EE16 transformer gapped core with an effective inductance  $A_{LE}$  of 117nH/T<sup>2</sup> is selected. The number of turns of the primary winding is:

$$N_{P} = \sqrt{\frac{L_{P}}{A_{IE}}} = \sqrt{\frac{2.3mH}{117 \text{ nH} / T^{2}}} = 140 \tag{11}$$

The number of turns of secondary and auxiliary windings can be derived accordingly:

$$N_S = \frac{N_S}{N_P} \times N_P = \frac{1}{14} \times 140 = 10$$

(12)

$$N_A = \frac{N_A}{N_C} \times N_S = 2.7 \times 10 = 27$$

(13)

The current sense resistance (R<sub>CS</sub>) determines the current limit value based on the following equation:

$$R_{\text{CS}} = \frac{0.9 \times V_{\text{CSLIM}}}{\sqrt{\frac{\left(I_{\text{OUTFL}} + I_{\text{OUTMAX}}\right) \times V_{\text{OUT}}}{\eta_{\text{xfm}}}}} = \frac{0.9 \times 0.396}{\sqrt{\frac{(0.7 + 0.9) \times 5}{2.35 \times 40 \times \left(\frac{0.69}{0.9}\right)}}} = 1.07R$$

(14)

Where Fsw is the frequency at CC mode.

The voltage feedback resistors are selected according to below equation:

$$R_{FB1} = \frac{N_A}{N_P} \times \frac{L_P}{R_{CS}} \times K = \frac{27}{140} \times \frac{2.35}{1.07} \times 126237 \approx 53.6k$$

(15)

Where K is IC constant and K = 126237.

$$R_{FB2} = \frac{V_{FB}}{(V_{OUTCV} + V_{DS}) \frac{N_A}{N_S} - V_{FB}} R_{FB1}$$

$$= \frac{2.20}{(5 + 0.3) \times 2.7 - 2.20} \times 53.6 = 9.76 k$$

(16)

When selecting the output capacitor, a low ESR electrolytic capacitor is recommended to minimize ripple from the current ripple. The approximate equation for the output capacitance value is given by:

$$C_{OUT} = \frac{I_{OUTCC}}{f_{SW} \times \triangle V_{RIPPLE}} = \frac{0.7}{42kHz \times 50mV} = 333 \mu F$$

(17)

A 470 $\mu$ F electrolytic capacitor is used to keep the ripple small.

#### **PCB Layout Guideline**

Good PCB layout is critical to have optimal performance. Decoupling capacitor (C3), current sense resistor (R7) and feedback resistor (R8/R9) should be placed close to  $V_{DD}$ , CS and FB pins respectively. There are two main power path loops. One is formed by C1/C2, primary winding, NPN transistor and the ACT361. The other is the secondary winding, rectifier D7 and output capacitors (C7). Keep these loop areas as small as possible. Connect high current ground returns, the input capacitor ground lead, and the ACT361 G pin to a single point (star ground configuration).

#### TYPICAL APPLICATION CONT'D

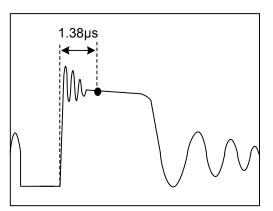

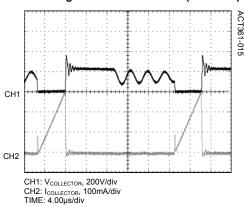

### **V<sub>FB</sub> Sampling Waveforms**

ACT361 senses the output voltage information through the  $V_{FB}$  waveforms. Proper  $V_{FB}$  waveforms are required for IC to operate in a stable status. To avoid mis-sampling, 1.38 $\mu$ s blanking time is added to blank the ringing period due to the leakage inductance and the circuit parasitic capacitance.

Figure 2 is the recommended  $V_{FB}$  waveform to guarantee the correct sampling point so that the output information can be sent back into the IC to do the appropriate control.

Figure 2:

Figure 3: Universal VAC Input, 5V/0.7A Output Charger

Table 1: ACT361 Bill of Materials

| ITEM | REFERENCE | DESCRIPTION                                   |   | MANUFACTURER |

|------|-----------|-----------------------------------------------|---|--------------|

| 1    | U1        | IC, ACT361US-T, SOT23-6                       |   | Active-Semi  |

| 2    | C1, C2    | Capacitor, Electrolytic, 4.7µF/400V, 8 × 12mm | 2 | KSC          |

| 3    | C3        | Capacitor, Electrolytic, 4.7µF/35V, 5 × 11mm  | 1 | POE          |

| 4    | C7        | Capacitor, Electrolytic, 470µF/10V, 8 × 12mm  | 1 | KSC          |

| 5    | D1-D4     | Diode, Rectifier, 1000V/1A, 1N4007, DO-41     | 4 | Good-Ark     |

| 6    | D5        | Diode, Ultra Fast, FR102,100V/1.0A, DO-41     | 1 | Good-Ark     |

| 7    | D7        | Diode, Schottky, 40V/2A, SB240, DO-15         | 1 | Good-Ark     |

| 8    | L1        | Axial Inductor, 1.5mH, 0410, DIP              | 1 | Amode Tech   |

| 9    | Q1        | Transistor, NPN, 900V,1.5A, KSB13003AR, TO-92 | 1 | Semi How     |

| 10   | FR1       | Fusible Resistor, 1W, 10Ω, 5%                 |   | TY-OHM       |

| 11   | R1, R2    | Chip Resistor, 5.1MΩ, 1206, 5%                |   | TY-OHM       |

| 12   | R4        | Chip Resistor, 150k, 0805, 5%                 | 1 | TY-OHM       |

| 13   | R5        | Chip Resistor, 22Ω, 0603, 5%                  | 1 | TY-OHM       |

| 14   | R7        | Chip Resistor, 1.07Ω, 1206, 1%                | 1 | TY-OHM       |

| 15   | R8        | Chip Resistor, 53.6k, 0805, 1%                | 1 | TY-OHM       |

| 16   | R9        | Chip Resistor, 9.76k, 0805, 1%                |   | TY-OHM       |

| 17   | R10       | Chip Resistor, 22Ω, 0805, 5%                  | 1 | TY-OHM       |

| 18   | R11       | Chip Resistor, 1.1k, 0805, 5%                 | 1 | TY-OHM       |

| 19   | T1        | Transformer, $L_P$ = 2.3mH±7%, EE16           | 1 |              |

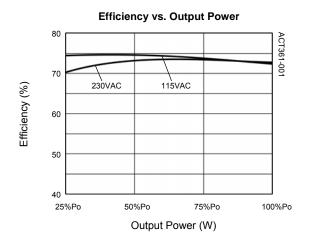

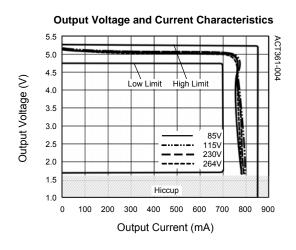

### TYPICAL PERFORMANCE CHARACTERISTICS

(Circuit of Figure 6, unless otherwise specified.)

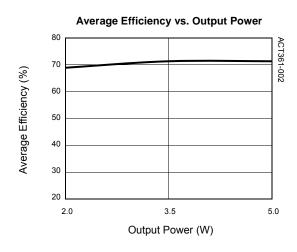

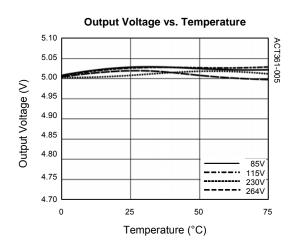

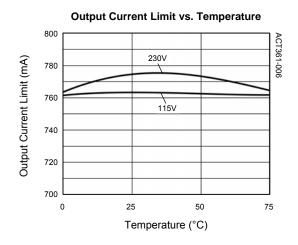

### TYPICAL PERFORMANCE CHARACTERISTICS CONT'D

(Circuit of Figure 6, unless otherwise specified.)

### TYPICAL PERFORMANCE CHARACTERISTICS CONT'D

(Circuit of Figure 6, unless otherwise specified.)

# Output Cable Resistance Compensation vs. Output Current

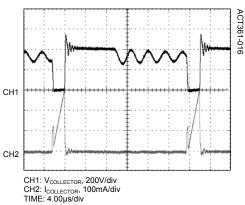

#### Switching Waveform at 115VAC (Full Load)

Switching Waveform at 230VAC (Full Load)

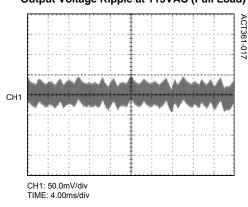

Output Voltage Ripple at 115VAC (Full Load)

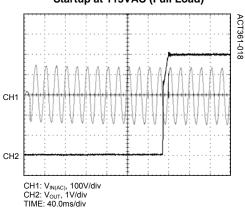

Startup at 115VAC (Full Load)

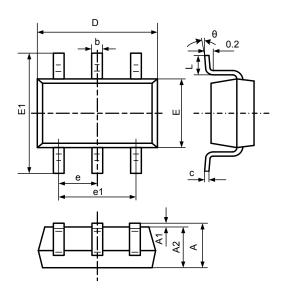

### **PACKAGE OUTLINE**

#### SOT23-6 PACKAGE OUTLINE AND DIMENSIONS

| SYMBOL | DIMENSION IN MILLIMETERS |       | DIMENSION IN INCHES |       |  |

|--------|--------------------------|-------|---------------------|-------|--|

|        | MIN                      | MAX   | MIN                 | MAX   |  |

| Α      | -                        | 1.450 | -                   | 0.057 |  |

| A1     | 0.000                    | 0.150 | 0.000               | 0.006 |  |

| A2     | 0.900                    | 1.300 | 0.035               | 0.051 |  |

| b      | 0.300                    | 0.500 | 0.012               | 0.020 |  |

| С      | 0.080                    | 0.220 | 0.003               | 0.009 |  |

| D      | 2.900                    | BSC   | 0.114 BSC           |       |  |

| Е      | 1.600                    | BSC   | 0.063 BSC           |       |  |

| E1     | 2.800                    | BSC   | 0.110 BSC           |       |  |

| е      | 0.950 BSC                |       | 0.037 BSC           |       |  |

| e1     | 1.900 BSC                |       | 0.075 BSC           |       |  |

| L      | 0.300                    | 0.600 | 0.012               | 0.024 |  |

| θ      | 0°                       | 8°    | 0°                  | 8°    |  |

Active-Semi, Inc. reserves the right to modify the circuitry or specifications without notice. Users should evaluate each product to make sure that it is suitable for their applications. Active-Semi products are not intended or authorized for use as critical components in life-support devices or systems. Active-Semi, Inc. does not assume any liability arising out of the use of any product or circuit described in this datasheet, nor does it convey any patent license.

Active-Semi and its logo are trademarks of Active-Semi, Inc. For more information on this and other products, contact sales@active-semi.com or visit <a href="http://www.active-semi.com">http://www.active-semi.com</a>.

octive-semi is a registered trademark of Active-Semi.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Qorvo:

ACT361US-T EA361US