# CHY100 ChiPhy™ Family

# Charger Interface Physical Layer IC

# **Product Highlights**

- Fully supports Quick Charge 2.0 specification

- Class A: 5 V, 9 V, and 12 V output voltage

- Class B: 5 V, 9 V, 12 V, and 20 V output voltage

- USB battery charging specification revision 1.2 compatible

- Automatic USB DCP shorting D+ to D- line

- Default 5 V mode operation

- · Supports TOPSwitch and TinySwitch

- · Very low power consumption

- Below 1 mW at 5 V output

- Fail safe operation

- · Adjacent pin-to-pin short-circuit fault

- · Open circuit pin fault

#### **Typical Applications**

- Battery chargers for smart phones, tablets, netbooks, digital cameras, and bluetooth accessories

- · USB power output ports

# Description

CHY100 is a low-cost USB high-voltage dedicated charging port (HVDCP) interface IC for the Quick Charge 2.0 specification. It incorporates all necessary functions to add Quick Charge 2.0 capability to Power Integrations' switcher ICs such as TOPSwitch or TinySwitch and other solutions employing traditional feedback schemes.

CHY100 supports the full output voltage range of either Class A or Class B. Optionally Class B can be inhibited for protecting the battery charger from accidental damage.

CHY100 automatically detects whether a connected Powered Device (PD) is Quick Charge 2.0 capable before enabling output voltage adjustment. If a PD not compliant to Quick Charge 2.0 is detected the CHY100 disables output voltage adjustment to ensure safe operation with legacy 5 V only USB PDs.

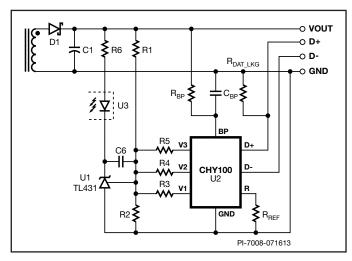

Figure 1. Typical Application Schematic.

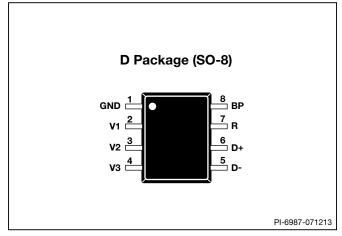

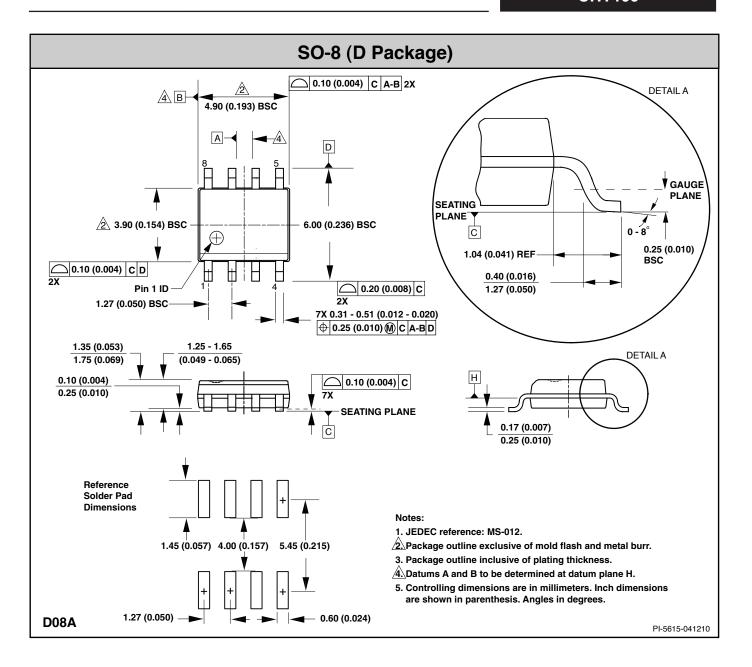

SO-8 (D Package)

Figure 2. Package Option.

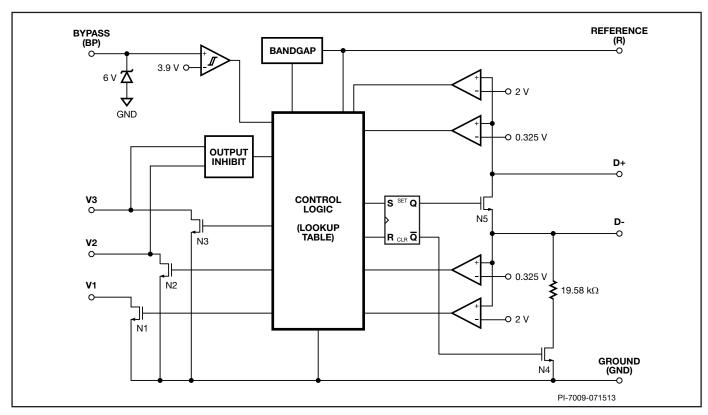

Figure 3. Functional Block Diagram.

#### **Pin Functional Description**

## GROUND (GND) Pin

Ground.

#### V1 Pin

Open Drain input of output voltage adjustment switch. Active for 9 V, 12 V, and 20 V output setting.

#### V2 Pir

Open Drain input of output voltage adjustment switch. Active for 12 V, and 20 V output setting.

#### V3 Pin

Open Drain input of output voltage adjustment switch. Active for 20 V output setting.

#### BYPASS (BP) Pin

Connection point for an external bypass capacitor for the internally generated supply voltage.

#### REFERENCE (R) Pin

Connected to internal band-gap reference. Provides reference current through connected resistor.

## DATA LINE D+ Pin

USB D+ data line input.

#### **DATA LINE D- Pin**

USB D- data line input.

Figure 4. Pin Configuration.

#### **Functional Description**

CHY100 is a low-cost USB high-voltage dedicated charging port (HVDCP) interface IC for the Quick Charge 2.0 specification. It incorporates all necessary functions to add Quick Charge 2.0 capability to Power Integrations' integrated switcher ICs such as TOPSwitch or TinySwitch.

CHY100 also supports other solutions with traditional feedback schemes like optocoupler and secondary reference regulator TL431 as depicted in Figure 5.

Figure 5. CHY100 with Traditional Output Regulation (CV Only).

CHY100 supports the full output voltage range of Quick Charge 2.0 Class A (5 V, 9 V, or 12 V) or Class B (5 V, 9 V, 12 V, or 20 V). It automatically detects either Quick Charge 2.0 capable powered devices (PD) or legacy PDs compliant with the USB Battery Charging Specification revision 1.2 and only enables output voltage adjustment accordingly.

#### **Shunt Regulator**

The internal shunt regulator clamps the BYPASS pin at 6 V when current is provided through an external resistor (R $_{\rm BP}$  in Figure 5). This facilitates powering of CHY100 externally over the wide power supply output voltage range of 5 V to 20 V. Recommended values are R $_{\rm BP}=4.53~{\rm k}\Omega$  and C $_{\rm BP}=220~{\rm nF}.$

#### **BYPASS Pin Undervoltage**

The BYPASS pin undervoltage circuitry resets the CHY100 when the BYPASS pin voltage drops below 3.9 V. Once the BYPASS pin voltage drops below 3.9 V it must rise back to 4 V to enable correct operation.

#### Reference Input

Resister R<sub>REF</sub> at the REFERENCE pin is connected to an internal band gap reference and provides an accurate reference current for internal timing circuits. The recommended value is  $R_{\text{REF}} = 127 \text{ k}\Omega$ .

#### Quick Charge 2.0 Interface

At power-up CHY100 turns on switch N5 (see Figure 3) in 20 ms or less after the BYPASS pin voltage has reached 4 V. Switch N4 and output switches N1 to N3 remain off. This sets the default 5 V output voltage level. With D+ and D- short-circuited the normal handshake between the AC-DC adapter (DCP) and powered devices (PD) as described in the USB Battery Charging Specification 1.2 can commence. After switch N5 has been turned on CHY100 starts monitoring the voltage level at D+. If it continuously stays above  $\rm V_{DAT(REF)}$  (typ. 0.325 V) and below  $\rm V_{SEL(REF)}$  (typ. 2 V) for at least 1.25 seconds CHY100 will enter Quick Charge 2.0 operation mode. If the voltage at D+ drops any time below 0.325 V CHY100 resets the 1.25 seconds timer and stays in USB Battery Charging Specification 1.2 compatibility mode with a default output voltage of 5 V.

Once CHY100 has entered Quick Charge 2.0 operation mode switch N5 will be turned off. Additionally switch N4 is turned on connecting a 19.53 k $\Omega$  pull-down resistor to D-. As soon as the voltage at D- has dropped low (<0.325 V) for at least 1 ms CHY100 starts accepting requests for different AC-DC adapter output voltages by means of applied voltage levels at data lines D+ and D- through the powered device. Table 1 summarizes the output voltage lookup table, corresponding AC-DC adapter output voltages and status of switches N1 to N3.

|       | <b>D</b> | 0             | Curitale Ctatus        |  |  |

|-------|----------|---------------|------------------------|--|--|

| D+    | D-       | Output        | Switch Status          |  |  |

| 0.6 V | 0.6 V    | 12 V          | N1 = N2 = On, N3 = Off |  |  |

| 3.3 V | 0.6 V    | 9 V           | N1 = On, N2 = N3 = Off |  |  |

| 3.3 V | 3.3 V    | 20 V          | N1 = N2 = N3 = On      |  |  |

| 0.6 V | GND      | 5 V (default) | N1 = N2 = N3 = Off     |  |  |

Table 1. Output Voltage Lookup Table.

For Quick Charge 2.0 Class A support only, the V3 pin has to be connected to the BYPASS pin (directly or through a resistor up to 100 k $\Omega$ ). This will inhibit any requests for setting a 20 V output.

At USB cable disconnect the voltage level at D+ is pulled down by resistor  $R_{\text{DAT(LKG)}}$  (see Figure 5). Once it drops below 0.325 V CHY100 will turn on switch N5 (thereby short-circuiting D+ and D-) and turns off switches N1 to N4. This sets the default output voltage of 5 V. The recommended value for  $R_{\text{DAT(LKG)}}=390~\text{k}\Omega.$

# **CHY100**

| Absolute Maximum Ratings        |                                                |

|---------------------------------|------------------------------------------------|

| BYPASS Pin Voltage0.3 to 9 V    | Operating Junction Temperature40 °C to +150 °C |

| REFERENCE Pin Voltage0.3 to 9 V | Operating Ambient Temperature40 °C to 105 °C   |

| V1/V2/V3 Pin Voltage0.3 to 9 V  | Storage Temperature65 °C to 150 °C             |

| D+/D- Pin Voltage0.3 to 5 V     | Lead Temperature <sup>(1)</sup> 260 °C         |

| BYPASS Pin Current              | Notes:                                         |

| V1/V2/V3 Pin Current            | 1. 1/16 in. from case for 5 seconds.           |

| D+/D- Pin Current               |                                                |

| Parameter                               | Symbol                           | Conditions SOURCE = 0 V; T <sub>J</sub> = -20 °C to +85 °C (Unless Otherwise Specified) | Min                  | Тур   | Max  | Units |

|-----------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|----------------------|-------|------|-------|

| Supply, Reference and I                 | Protection F                     | unctions                                                                                |                      |       |      |       |

| BYPASS Pin Voltage                      | $V_{BP}$                         |                                                                                         | 4                    | 5     | 6    | V     |

| Power-Up Reset<br>Threshold Voltage     | V <sub>BP(RESET)</sub>           |                                                                                         | 2.0                  |       | 3.9  | V     |

| BYPASS Pin<br>Source Current            | I <sub>BPSC</sub>                | $V_{BP} = 4.3 \text{ V, T}_{J} = 25 \text{ °C}$<br>N1 = N2 = N3 = Off                   |                      |       | 135  | μА    |

| BYPASS Pin<br>Shunt Voltage             | V <sub>BP(SHUNT)</sub>           | I <sub>BP</sub> = 3 mA                                                                  | 5.7                  | 6     | 6.3  | V     |

| REFERENCE Pin<br>Voltage                | $V_{R}$                          |                                                                                         | 1.18                 | 1.23  | 1.28 | V     |

| HVDCP Functions                         |                                  |                                                                                         |                      |       |      | ,     |

| Data Detect Voltage                     | $V_{\text{DAT(REF)}}$            |                                                                                         | 0.25                 | 0.325 | 0.4  | V     |

| Output Voltage<br>Selection Reference   | $V_{\text{SEL(REF)}}$            |                                                                                         | 1.8                  | 2     | 2.2  | V     |

| 12 V / 20 V Output<br>Inhibit Threshold | V <sub>INH</sub>                 |                                                                                         | V <sub>BP</sub> -0.6 |       |      | V     |

| Data Lines<br>Short-Circuit Delay       | T <sub>DAT(SHORT)</sub>          | V <sub>OUT</sub> ≥ 0.8 V<br>See Figure 5                                                |                      | 10    | 20   | ms    |

| D+ High Glitch<br>Filter Time           | T <sub>GLITCH(BC)</sub>          |                                                                                         | 1000                 | 1250  | 1500 | ms    |

| Output Voltage<br>Glitch Filter Time    | T <sub>GLITCH(V)</sub><br>CHANGE |                                                                                         | 20                   | 40    | 60   | ms    |

| D- Pull-Down<br>Resistance              | $R_{\text{DM(DWN)}}$             |                                                                                         | 14.25                | 19.53 | 24.5 | kΩ    |

| Switch N1<br>On-Resistance              | R <sub>DS(ON)N1</sub>            | I <sub>N1</sub> = 200 μA                                                                |                      |       | 300  | Ω     |

| Switch N2<br>On-Resistance              | R <sub>DS(ON)N2</sub>            | I <sub>N2</sub> = 200 μA                                                                |                      |       | 300  | Ω     |

| Switch N3<br>On-Resistance              | R <sub>DS(ON)N3</sub>            | I <sub>N3</sub> = 200 μA                                                                |                      |       | 300  | Ω     |

| Switch N4<br>On-Resistance              | R <sub>DS(ON)N4</sub>            | I <sub>N4</sub> = 200 μA                                                                |                      |       | 300  | Ω     |

| Switch N5<br>On-Resistance              | R <sub>DS(ON)N5</sub>            | $I_{N5} = 200 \ \mu A, \ V_{(D+)} \le 3.6 \ V$                                          |                      | 20    | 40   | Ω     |

| Data Line Capacitance                   | C <sub>DCP(PWR)</sub>            | See Note A                                                                              |                      |       | 1    | nF    |

# NOTES:

A. Guaranteed by design. Not tested in production.

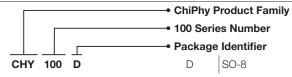

# **Part Ordering Information**

| Revision | Notes                                     | Date  |

|----------|-------------------------------------------|-------|

| А        | Initial Release.                          | 07/13 |

| В        | Extended Ambient Temperature to -40 °C.   | 01/14 |

| С        | Added Note for Class A Charger on page 3. | 03/14 |

#### For the latest updates, visit our website: www.powerint.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **Patent Information**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

#### **Life Support Policy**

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The PI logo, TOPSwitch, TinySwitch, LinkSwitch, LYTSwitch, DPA-Switch, PeakSwitch, CAPZero, SENZero, LinkZero, HiperPFS, HiperTFS, HiperLCS, Qspeed, EcoSmart, Clampless, E-Shield, Filterfuse, StakFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2014, Power Integrations, Inc.

# **Power Integrations Worldwide Sales Support Locations**

# World Headquarters 5245 Hellyer Avenue San Jose, CA 95138, USA. Main: +1-408-414-9200 Customer Service: Phone: +1-408-414-9665 Fax: +1-408-414-9765 e-mail: usasales@powerint.com

#### China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 Fax: +86-21-6354-6325 e-mail: chinasales@powerint.com

#### China (ShenZhen)

3rd Floor, Block A, Zhongtou International Business Center, No. 1061, Xiang Mei Rd, FuTian District, ShenZhen, China, 518040

Phone: +86-755-8379-3243 Fax: +86-755-8379-5828

e-mail: chinasales@powerint.com

#### Germany

Lindwurmstrasse 114 80337 Munich Germany Phone: +49-895-527-39110

Fax: +49-895-527-39200 e-mail: eurosales@powerint.com

#### India

Vasanthanagar Bangalore-560052 India Phone: +91-80-4113-8020 Fax: +91-80-4113-8023 e-mail: indiasales@powerint.com

#1, 14th Main Road

#### Italy

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy

Phone: +39-024-550-8701 Fax: +39-028-928-6009 e-mail: eurosales@powerint.com

## Japan

Kosei Dai-3 Bldg. 2-12-11, Shin-Yokohama, Kohoku-ku Yokohama-shi Kanagwan

222-0033 Japan Phone: +81-45-471-1021

Fax: +81-45-471-3717 e-mail: japansales@powerint.com

# Korea

RM 602, 6FL Korea City Air Terminal B/D, 159-6 Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea

Phone: +82-2-2016-6610 Fax: +82-2-2016-6630 e-mail: koreasales@powerint.com

#### Singapore

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160

Fax: +65-6358-2015

e-mail: singaporesales@powerint.com

#### Taiwan

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist. Tainei 11493 Taiwan B O C

Taipei 11493, Taiwan R.O.C. Phone: +886-2-2659-4570 Fax: +886-2-2659-4550

e-mail: taiwansales@powerint.com

#### Europe HQ

1st Floor, St. James's House East Street, Farnham Surrey GU9 7TJ United Kingdom

Phone: +44 (0) 1252-730-141 Fax: +44 (0) 1252-727-689 e-mail: eurosales@powerint.com

#### Applications Hotline

World Wide +1-408-414-9660

# Applications Fax

World Wide +1-408-414-9760

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Power Integrations: CHY100D-TL CHY100D

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Power Integrations: CHY100D-TL